JRC Scientific and Technical Reports

# The Future of Semiconductor Intellectual Property Architectural Blocks in Europe

Author: Ilkka Tuomi Editor: Marc Bogdanowicz

EUR 23962 EN - 2009

The Future of Semiconductor Intellectual Property Architectural Blocks in Europe

Author: Ilkka Tuomi

Editor: Marc Bogdanowicz

2009

EUR 23962 EN

The mission of the JRC-IPTS is to provide customer-driven support to the EU policy-making process by developing science-based responses to policy challenges that have both a socio-economic as well as a scientific/technological dimension.

#### **European Commission**

Joint Research Centre Institute for Prospective Technological Studies

#### **Contact information**

Address: Edificio Expo. c/ Inca Garcilaso, 3. E-41092 Seville (Spain) E-mail: jrc-ipts-secretariat@ec.europa.eu Tel.: +34 954488318 Fax: +34 954488300

> http://ipts.jrc.ec.europa.eu http://www.jrc.ec.europa.eu

#### Legal Notice

Neither the European Commission nor any person acting on behalf of the Commission is responsible for the use which might be made of this publication.

#### Europe Direct is a service to help you find answers to your questions about the European Union

#### Freephone number (\*): 00 800 6 7 8 9 10 11

(\*) Certain mobile telephone operators do not allow access to 00 800 numbers or these calls may be billed.

A great deal of additional information on the European Union is available on the Internet. It can be accessed through the Europa server http://europa.eu/

#### JRC52422

EUR 23962 EN Catalogue number: LF-NA-23962-EN-C ISSN: 1018-5593 ISBN: 978-92-79-13058-8 DOI: 10.2791/13315

Luxembourg: Office for Official Publications of the European Communities

© European Communities, 2009

Reproduction is authorised provided the source is acknowledged Printed in Spain

Over the last decades, developed economies have been undergoing a structural transformation towards knowledge economies. Trends include:

- A growing and now dominant share of the economy represented by "services",

- Extended and sustained growth of knowledge assets with supporting changes in R&D activities, education, lifelong learning, etc,

- A shift in the economic activity of developed economies to concentrate on the higher levels of the value chain. Manufacturing diminishes as a percentage of total output, often moving rapidly to lower-cost locations (mainly Asia).

Throughout the brief 50 year history of the semiconductor industry, its innovation and growth have been fuelled by rapid technical evolution. This has led to changes in the structure of the industry that have many similarities with those in the wider economy. In particular, the ownership and trading of intellectual property and the respective innovative business models have not only been hot topics of discussion at conferences and workshops but have also led to the creation of new industry segments. Over the past two decades, structural changes in the semiconductor "value chain" have led to the emergence of businesses dedicated to the development of computing cores which have rapidly proliferated into a very diverse range of consumer products.

Indeed, I was employed as a designer in the IC industry 30 years ago and was responsible for the development of one of the first commercially available CMOS cell libraries. Although this was a rudimentary predecessor of the IP cores and function blocks available today, many of the technical and commercial questions remain, albeit with many magnitude changes in complexity. Trade-offs between development time and costs, and between custom-dedicated and programmable must be weighed up. Factors such as optimisation of chip size, yield, cost, maximizing function, minimizing power consumption vs. redundancy, flexibility and programmability must also be carefully considered at the conception of a new product design and debates are even more complex and intense today than they were one or two decades ago.

IP-centric, fab-less companies are essential actors in the value chain. Hardware commoditisation has converted architectural IP and software into the main differentiation factors, and IP-centred companies into essential actors in the semiconductor industry value chain. The progressive relocation (to Asia) of the foundry companies, and consequently that of IP-centred activities close to their test sites (*"the fab is the lab"*) and also close to their markets (corporate manufacturing sector users: automotive, telco equipment, etc.), questions the very viability of European IP-centred companies and, in more general terms, the move to the higher levels of the value chain. The projected end of semiconductor scaling is posing additional vital challenges to the whole sector.

This report reflects the findings of the study, carried out by JRC-IPTS at the request of DG Information Society and Media, on the IP-centred industry. The report offers insights into the intellectual property business, and discusses the changing role of "drivers", including the emergence of Asian actors and the potential impact that may result as we approach limits in terms of technology scaling. It concludes by discussing the competitiveness of the European IP-centred industry and the policy-related issues that may impact future competence development, access to design tools, relevance of roadmap activities, intellectual property legislation, and emerging innovation models.

David Broster Head of the Information Society Unit JRC IPTS

# Table of Contents

#### 1. Executive Summary

# 2. Introduction112.1. Study Theme and Motivation112.1.1. European Intellectual Property Architectures in the Global Context122.2. Scope of the Study13

| 3. | 3. Emerging Discontinuities                 |    |

|----|---------------------------------------------|----|

|    | 3.1. The New Paradigm of Knowledge Economy  | 18 |

|    | 3.2. Innovation Communities and Ecosystems  | 22 |

|    | 3.3. Policy at the End of Kondratieff Waves | 23 |

| 4. | The Current Context of the Intellectual Property Architectural Blocks Industry | 27 |

|----|--------------------------------------------------------------------------------|----|

|    | 4.1. The Semiconductor Value System                                            | 27 |

|    | 4.1.1. Overview of Semiconductor Consumption and Production                    | 27 |

|    | 4.1.2. Current Business Models                                                 | 29 |

|    | 4.1.3. The Semiconductor Value Chain                                           | 38 |

| 5. | The  | e Intellectual Property Business                         | 43 |

|----|------|----------------------------------------------------------|----|

|    | 5.1. | The IP Market                                            | 43 |

|    | 5.2. | IP Customers                                             | 44 |

|    | 5.3. | IP Providers                                             | 47 |

|    |      | 5.3.1 Top 20 IP Core Vendors                             | 50 |

|    |      | 5.3.2. The Geographic Dimension                          | 53 |

|    | 5.4  | An In-Depth Look at Swedish IP Vendors                   | 60 |

|    |      | 5.4.1. Description of the Swedish IP Vendors             | 61 |

|    | 5.5  | Where Did the IP Vendors Come From? The Innovation Model | 64 |

|    |      | 5.5.1. The Case of ARM Holdings                          | 64 |

| 6. | His | torical | Drivers in the Intellectual Property Architectural Blocks Industry | 67 |

|----|-----|---------|--------------------------------------------------------------------|----|

|    | 6.1 | Semic   | onductor Scaling                                                   | 67 |

|    |     | 6.1.1.  | The End of Scaling                                                 | 71 |

|    |     | 6.1.2.  | The Long Tail of Semiconductor Products                            | 71 |

9

G Technical Report Series

| 6.2. Manufacturing and Design Costs             | 73 |

|-------------------------------------------------|----|

| 6.3. Local Ecosystems and the Asian Competition | 76 |

| 6.3.1. The Local Global Hub: Silicon Valley     | 76 |

| 6.3.2. The Move to Asia                         | 79 |

| 7. Makimoto Waves, Dominant Designs and User Innovation |                                                   | 85 |

|---------------------------------------------------------|---------------------------------------------------|----|

|                                                         | 7.1. Learning and Obsolescence in the IC Industry | 85 |

|                                                         | 7.2. Cycles of Standardization and Customization  | 87 |

|                                                         | 7.3. Configurability and Recombination            | 91 |

| 8. | Chi  | na as a | Creator of Future Intellectual Property Architectural Blocks | 97  |

|----|------|---------|--------------------------------------------------------------|-----|

|    | 8.1. | The St  | ate of the IC Market                                         | 97  |

|    | 8.2. | IC Des  | sign in China                                                | 102 |

|    |      | 8.2.1.  | Design Capabilities                                          | 103 |

|    | 8.3. | Policy  | Issues                                                       | 106 |

|    |      | 8.3.1.  | Export Regulations                                           | 106 |

|    |      | 8.3.2.  | Labour Contract Law                                          | 107 |

|    |      | 8.3.3.  | Investment Incentives and the New Corporate Income Tax       | 108 |

|    | 8.4. | The Fi  | ve Paths to the Chinese IP Future                            | 110 |

|    |      | 8.4.1.  | Manufacturing Pull                                           | 110 |

|    |      | 8.4.2.  | Large-Market Pull                                            | 111 |

|    |      | 8.4.3.  | Development Policy                                           | 114 |

|    |      | 8.4.4.  | Competence and Innovation System                             | 115 |

|    |      | 8.4.5.  | Technical Disruption                                         | 116 |

|    |      |         |                                                              |     |

| 9. | Policy Imp           | olications                                                              | 119 |

|----|----------------------|-------------------------------------------------------------------------|-----|

|    | 9.1. Four Key Trends |                                                                         |     |

|    | 9.2. Policy          | Alternatives                                                            | 121 |

|    | 9.2.1.               | Competence Development                                                  | 121 |

|    | 9.2.2.               | Expanded Access to Design Tools                                         | 122 |

|    | 9.2.3.               | Low-Cost Design Realisation Capabilities                                | 122 |

|    | 9.2.4.               | New Design Advantages                                                   | 123 |

|    | 9.2.5.               | Characterisation of Latent Demand and Supply Through Roadmap Activities | 123 |

|    | 9.2.6.               | Intellectual Property Legislation                                       | 124 |

|    | 9.2.7.               | Ecosystem Openness and New Innovation Models                            | 124 |

# 10. References

125

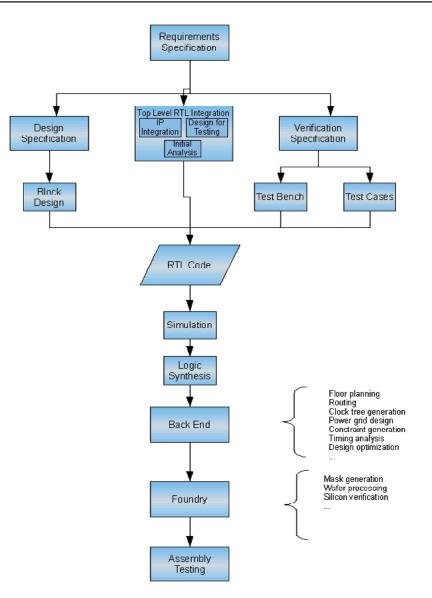

| 11. Appendix: The IC Design Process | 133 |

|-------------------------------------|-----|

| 11.1. The ASIC Design Flow          | 136 |

| 11.2. The FPGA Design Flow          | 138 |

### List of Tables

| Table 1:  | Semiconductor IP in 2008, as categorised by Gartner Inc.        | 15 |

|-----------|-----------------------------------------------------------------|----|

| Table 2:  | Integrated circuit market, 2007-2010, WSTS Autumn 2008 estimate | 28 |

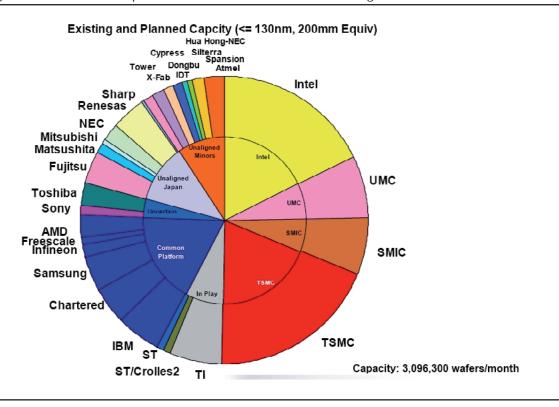

| Table 3:  | Top 10 foundries by revenue, 2007                               | 31 |

| Table 4:  | Top 20 semiconductor vendors in 2008                            | 33 |

| Table 5:  | Typical semiconductor IP licensing models.                      | 35 |

| Table 6:  | Main criteria for semiconductor IP make-or-buy decisions.       | 45 |

| Table 7:  | Top 20 IP vendor revenues and average employee counts, 2007     | 51 |

| Table 8:  | Top 20 IP firms with locus of activity in Europe.               | 59 |

| Table 9:  | Swedish IP vendors, revenues, profits, and employment.          | 61 |

| Table 10: | Top 10 design houses in China based on revenues in 2007         | 10 |

## List of Figures

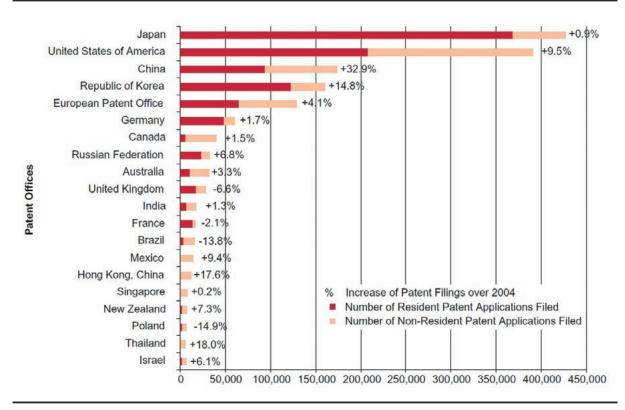

| Figure 1:  | Resident and non-resident patent applications in different countries, 2005       | 19 |

|------------|----------------------------------------------------------------------------------|----|

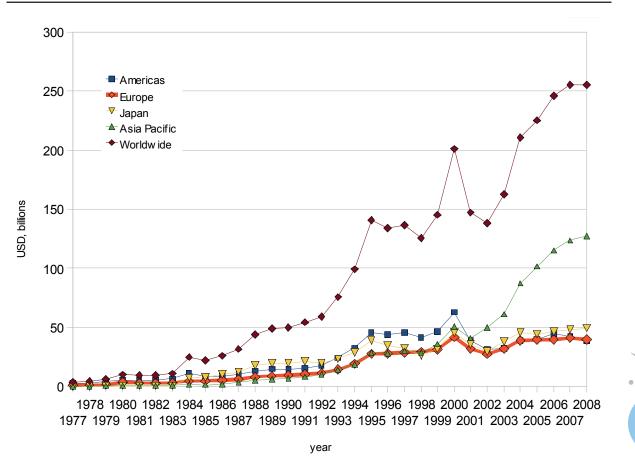

| Figure 2:  | Billings by semiconductor firms in different regions, 1977-2008                  | 27 |

| Figure 3:  | Alliance landscape in semiconductor wafer manufacturing                          | 32 |

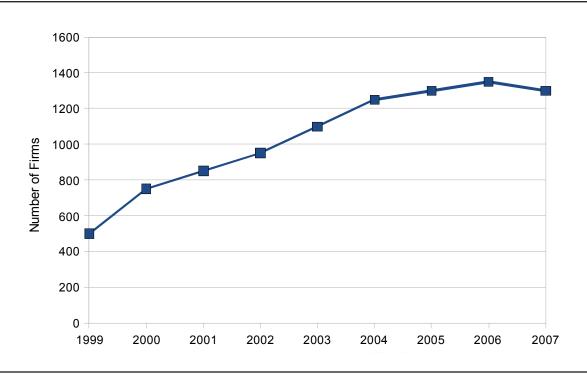

| Figure 4:  | Fabless semiconductor firms, 1999-2007                                           | 33 |

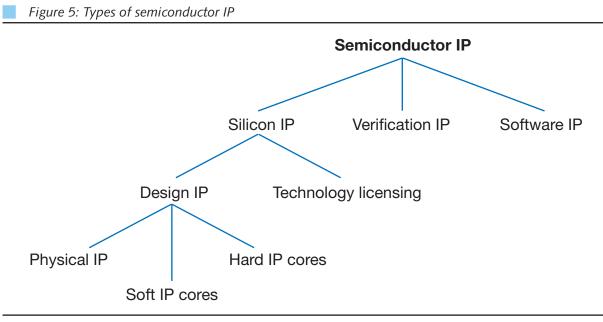

| Figure 5:  | Types of semiconductor IP                                                        | 37 |

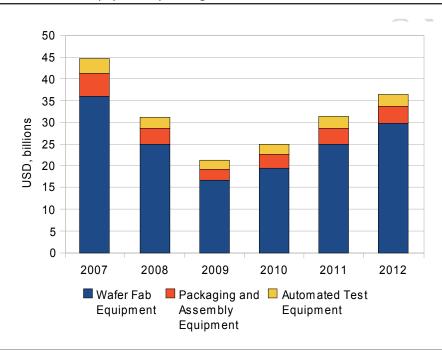

| Figure 6:  | Semiconductor equipment spending, 2007-2012                                      | 39 |

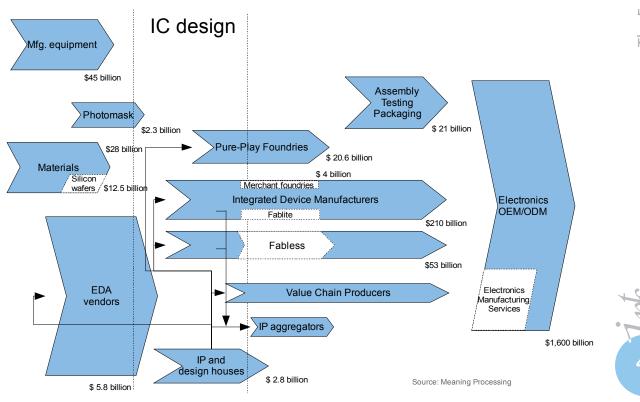

| Figure 7:  | The semiconductor value chain, 2007.                                             | 41 |

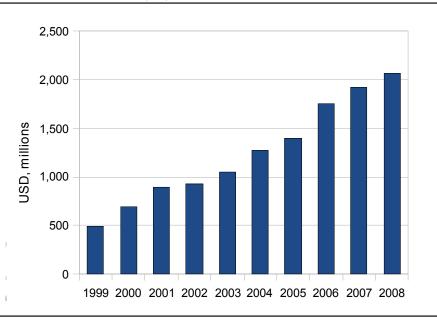

| Figure 8:  | Semiconductor intellectual property market, 1999-2008                            | 43 |

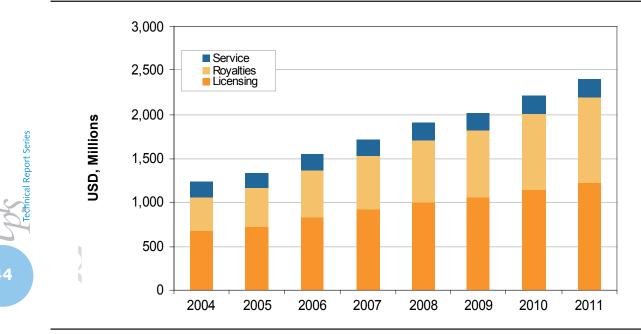

| Figure 9:  | iSuppli semiconductor IP revenue forecast, 2004-2011                             | 44 |

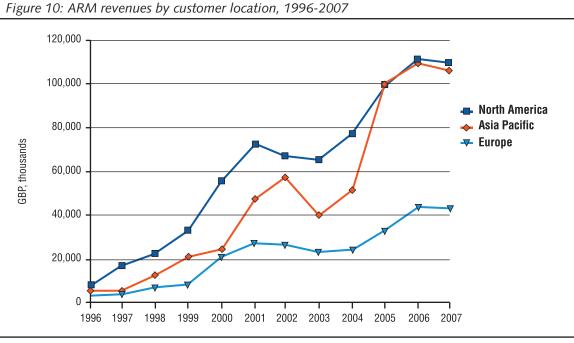

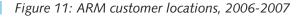

| Figure 10: | ARM revenues by customer location, 1996-2007                                     | 46 |

| Figure 11: | ARM customer locations, 2006-2007                                                | 46 |

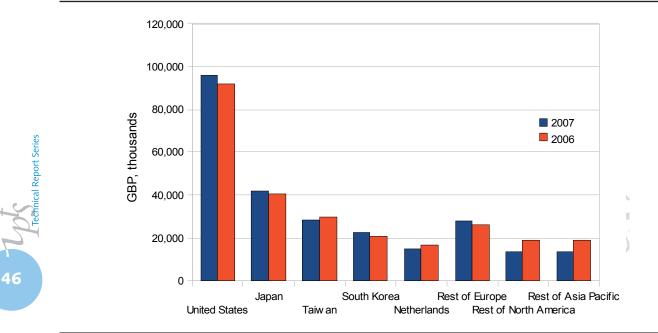

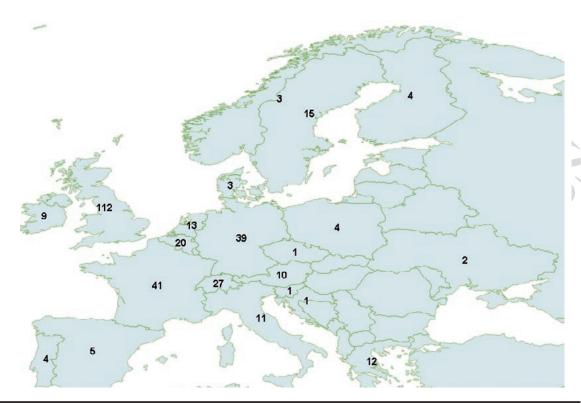

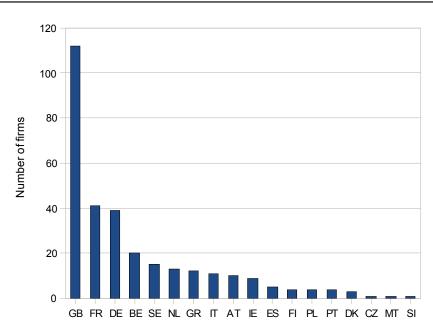

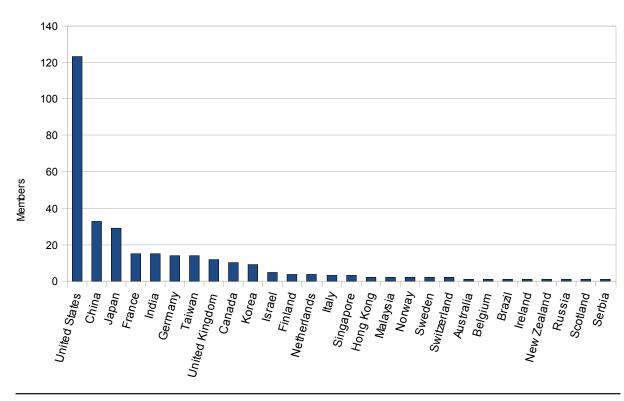

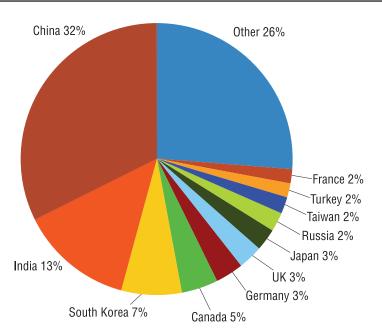

| Figure 12: | Geographic distribution of semiconductor IP creators                             | 53 |

| Figure 13: | Semiconductor IP vendors in the US.                                              | 54 |

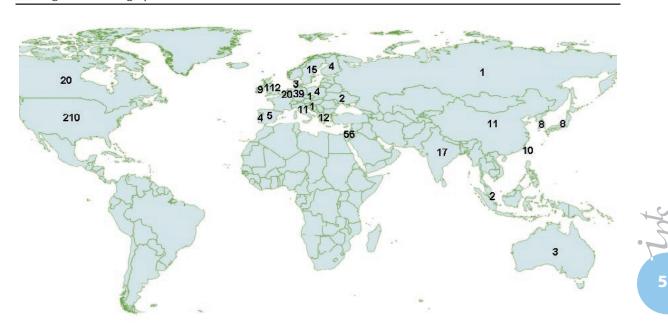

| Figure 14: | Fabless semiconductor firms, design houses, and IP vendors in Europe.            | 55 |

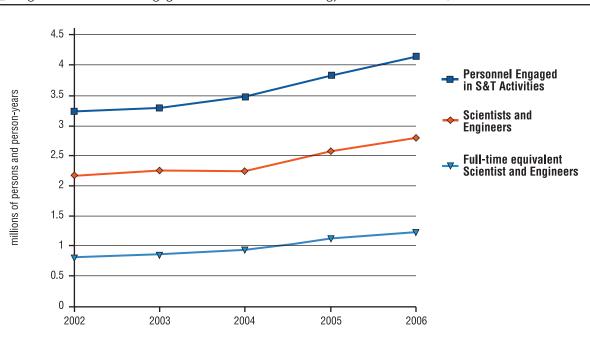

| Figure 15: | Fabless semiconductor firms, design houses and IP vendors headquartered in EU27, |    |

|            | year 2008.                                                                       | 55 |

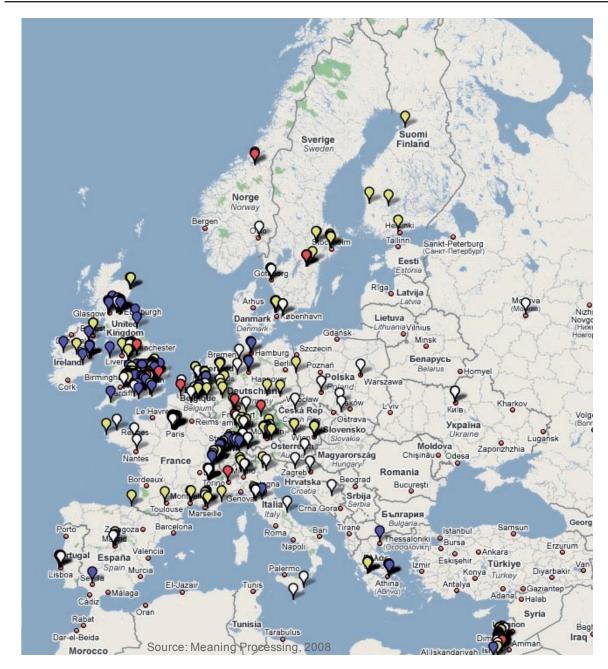

| Figure 16: | Locations of chipless firms in Europe.                                           | 57 |

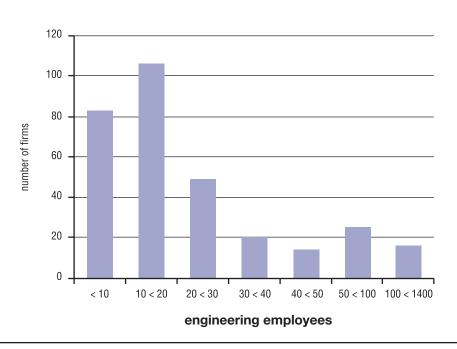

| Figure 17: | Number of engineers employed by European semiconductor design and IP firms.      | 59 |

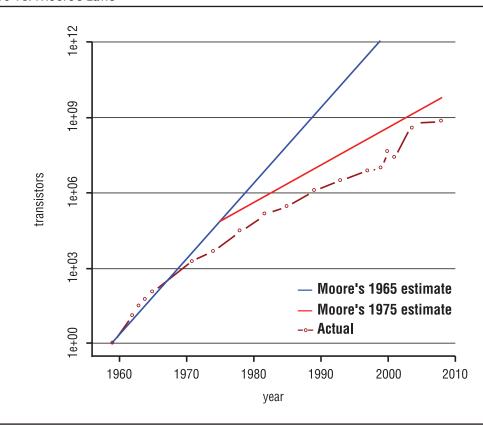

| Figure 18: | Moore's Laws                                                                     | 68 |

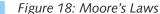

| Figure 19: | Year of introduction for process line widths                                     | 69 |

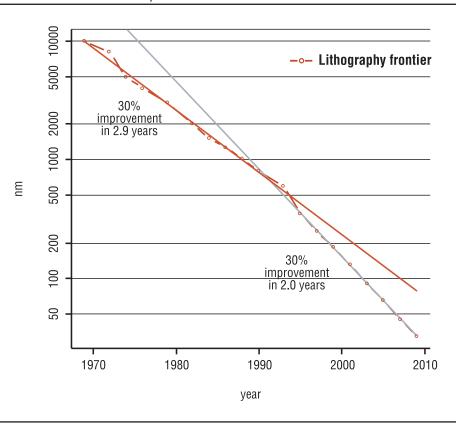

| Figure 20: | Constant-quality prices for microprocessors and DRAM memories                    | 70 |

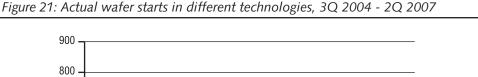

| Figure 21: | Actual wafer starts in different technologies, 3Q 2004 - 2Q 2007                 | 72 |

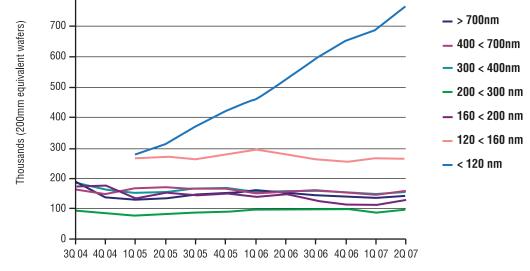

| Figure 22: | The long tail of semiconductor technology, 2008                                  | 73 |

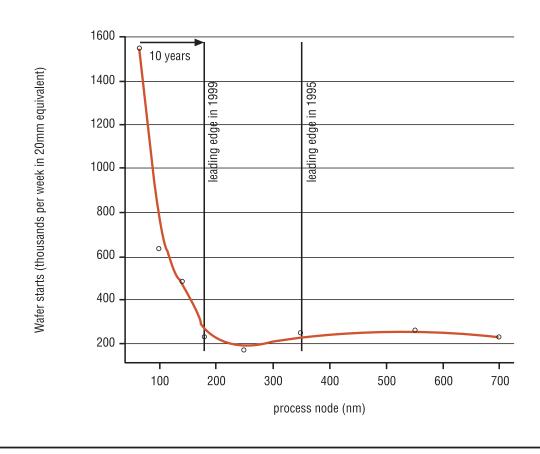

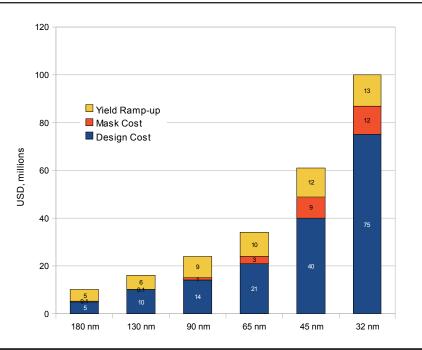

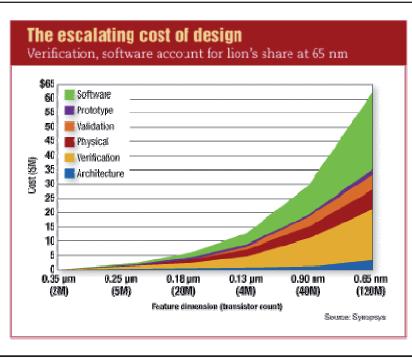

| Figure 23: | IC design costs at different process nodes                                       | 75 |

| Figure 24: | Design cost breakdown                                                            | 75 |

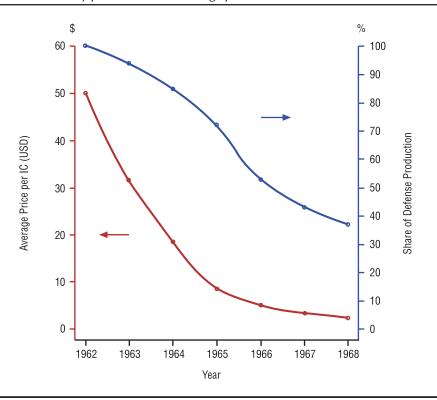

| Figure 25: | Share of military production and average price of ICs in the US 1962-1968        | 77 |

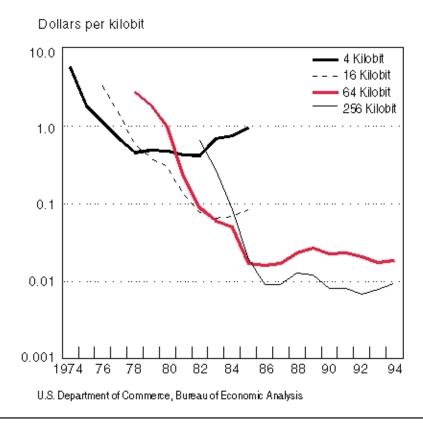

| Figure 26: | Price dynamics in different DRAM technology generations, 1974-1994               | 86 |

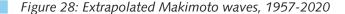

| Figure 27: | The Makimoto pendulum                                                            | 88 |

| Figure 28: | Extrapolated Makimoto waves, 1957-2020                                           | 89 |

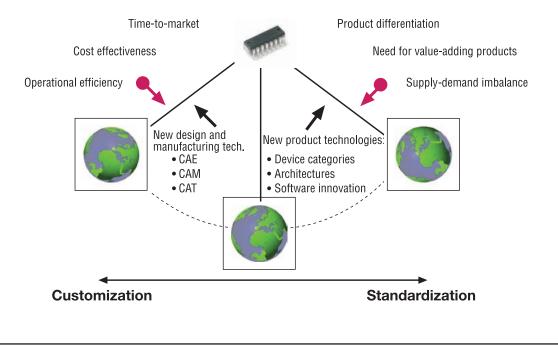

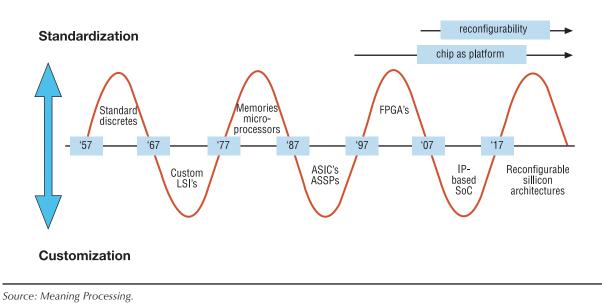

| Figure 29: | Innovation drivers in new product categories                                     | 92 |

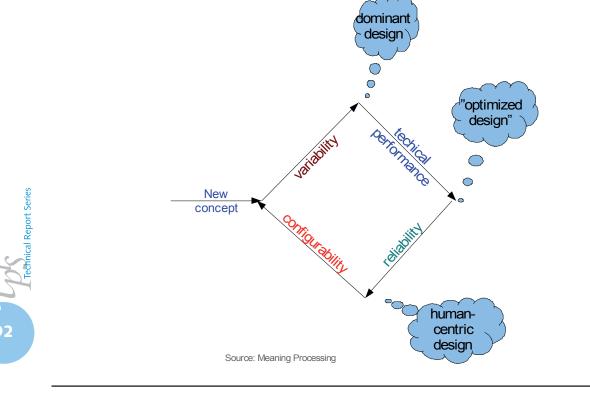

| Figure 30: | Production of integrated circuits in China, 1990-2007                            | 98 |

L Technical Report Series

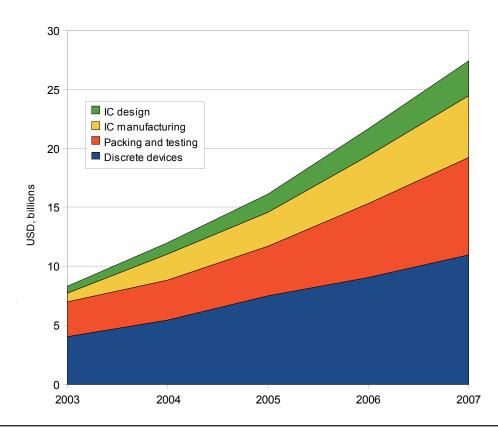

| Figure 31: China semiconductor revenues by industry sector, 2003-2007                                                       | 99  |

|-----------------------------------------------------------------------------------------------------------------------------|-----|

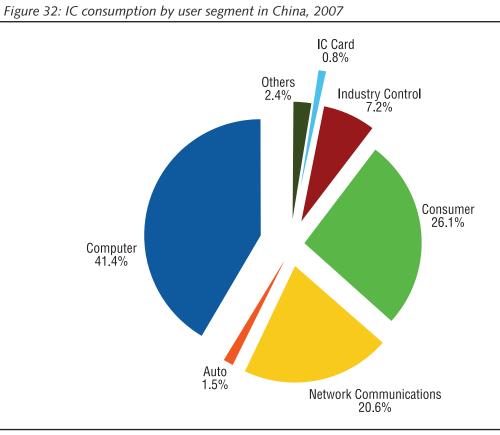

| Figure 32: IC consumption by user segment in China, 2007                                                                    | 100 |

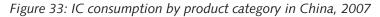

| Figure 33: IC consumption by product category in China, 2007                                                                | 100 |

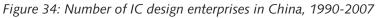

| Figure 34: Number of IC design enterprises in China, 1990-2007                                                              | 104 |

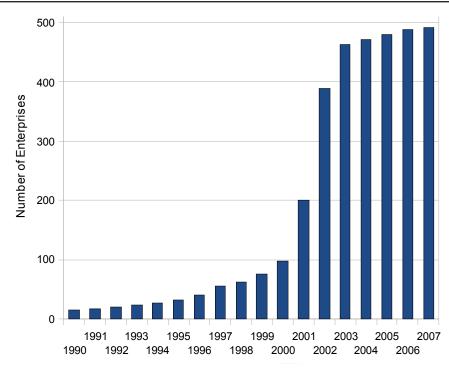

| Figure 35: Distribution of enterprise sizes in Chinese and European design firms                                            | 104 |

| Figure 36: ARM Connected Community members in different countries, 2008                                                     | 105 |

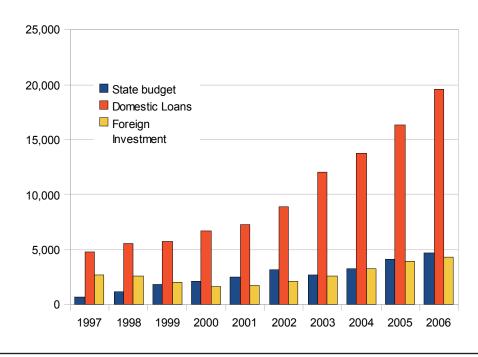

| Figure 37: Total investment in fixed assets in China                                                                        | 109 |

| Figure 38: Personnel engaged in science and technology activities in China, 2002-2006                                       | 112 |

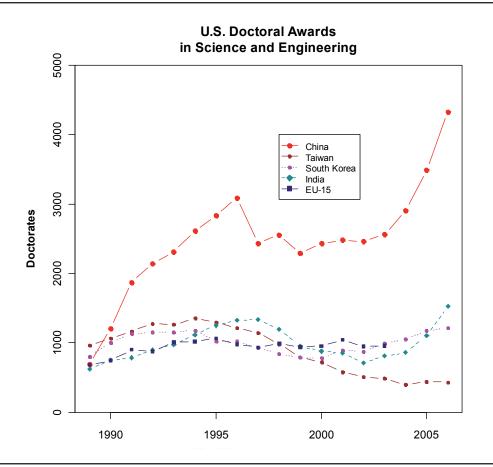

| Figure 39: PhDs in science and engineering from US institutions for Chinese citizens, 1989-2006                             | 113 |

| <i>Figure 40: Country of citizenship for new recipients of U.S. H-1B temporary work visas holding doctorates in FY 2006</i> | 113 |

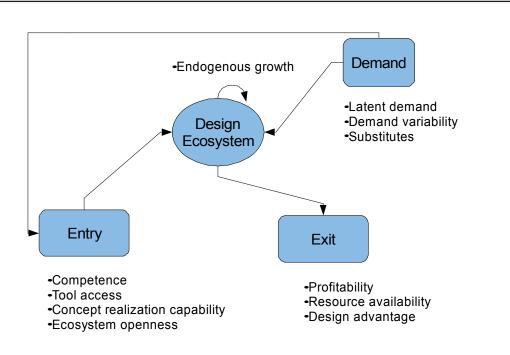

| Figure 41: Dynamics of the IP design ecosystem                                                                              | 121 |

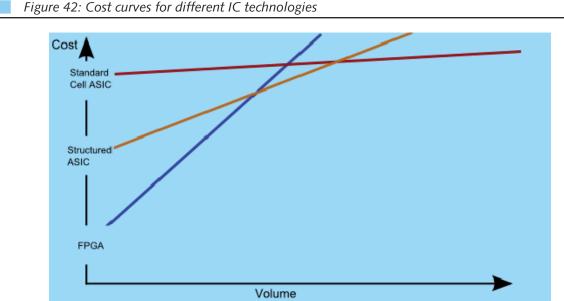

| Figure 42: Cost curves for different IC technologies                                                                        | 134 |

| Figure 43: The ASIC production flow                                                                                         | 136 |

| Figure 44: VHDL code for a logic OR circuit                                                                                 | 137 |

| Figure 45: Metal layers in a simple logic cell; 3D CAD image                                                                | 137 |

| Figure 46:Production flows for FPGA and ASIC                                                                                | 138 |

# 1. Executive Summary

During 2008 and 2009, the Information Society Unit of the Institute for Prospective Technological Studies<sup>1</sup> ran a research project on semiconductor intellectual property (IP) blocks, also known as IP cores. This project was launched at the request of the Directorate General Information Society and Media of the European Commission, and the research was conducted by Oy Meaning Processing Ltd. The study collects and analyses data on IP blocks, with a special focus on the future competitiveness of the related European industry.

Semiconductor intellectual property (IP) blocks, also known as IP cores, are reusable design components that are used to build advanced integrated circuits (ICs). It is typically impossible to create new IC designs without pre-designed IP blocks as a starting point. These design components are called "intellectual property" blocks because they are traded as rights to use and copy the design. Firms that focus on this business model are often called "chipless" semiconductor firms.

IP cores are perhaps the most knowledgeintensive link in the information economy value chain. They define the capabilities of billions of electronic devices produced every year. As all products are becoming increasingly intelligent and embedded with information processing and communication capabilities, future developments in semiconductor IP will have a profound impact on the future developments in the overall knowledge economy and society.

1 The Institute for Prospective Technological Studies is one of the seven research Institutes of the European Commission's Joint Research Centre. At present, the IC industry is approaching the most fundamental technological disruption in its history. The rapid incremental innovation that has led to exponential growth in the number of transistors on a chip and expanded the applications of ICT to all areas of human life is about to end. This discontinuity –the end of semiconductor scaling– opens up new business opportunities and shifts the focus of ICT research to new areas.

The main objective of this study is to describe the current state and potential future developments in semiconductor IP, and to relate the outcomes of the study to policy-related discussions relevant to the EU and its Member States.

Key results of the study include the following:

There are over 150 European firms that license semiconductor IP. Globally, among the top 20 independent IP vendors, nine have headquarters in the EU or have substantial development activities in European countries. At present, many IP vendors have difficulties with profitability and growth. The approaching technology disruption will, however, create new business models and potentially lead to rapid expansion of innovative activities in semiconductor-based industries.

Asian countries are implementing focused policies that aim to create and support semiconductor ecosystems that span from design to final system production. China –the largest semiconductor consumer worldwide– is still catching up technology leaders both in design and chip fabrication. The slowing down of advances in IC fabrication technology will, however, make this lag increasingly unimportant. There are now about 500 semiconductor design enterprises in China, although only a handful are actively marketing their IP outside China. China may be relatively well positioned for the new business logic and IP architectures that emerge at the end of semiconductor scaling in the next years.

Product reconfigurability is also becoming increasingly important in semiconductor hardware. Reconfigurability means that processing architecture can be changed according to the needs of the computational problem at hand. This will change the traditional division of labour between software and hardware, and make highperformance computation possible with relatively low-performance processing technologies.

When reconfigurable application-specific hardware architectures are combined with low cost implementation technologies, radically new domains of innovation become possible in the ICT industry. New downstream innovation models will become important. The realisation of emerging opportunities will, however, critically depend on wide access to design tools and competences. To a significant extent, the future of semiconductor IP depends on competence development that occurs in open innovation ecosystems and outside formal educational settings.

Several entry barriers limit growth in this area. Research policies that encourage the development of open design ecosystems, lowdesign-to-implementation cost paths, new forms of competence development, and new computational models could have high impact on the future of IP architectures in Europe. As the IP industry and its knowledge processes are based on global networks, regional policies have to be formulated in a global context, for example, as policies that facilitate the formation of strategic ecosystem hot-spots. In Chapter 9, the report suggests several concrete initiatives that could support policymaking and accelerate growth in this domain.

11

# 2. Introduction

#### 2.1. Study Theme and Motivation

This study describes the current state and future development scenarios for pre-designed semiconductor intellectual property cores (IP cores). IP cores, also known as IP blocks and "virtual components," are designs that can be used to build integrated semiconductor devices and "systems-on-chip." They are widely marketed by European, American and Asian firms, and they are critically important building blocks in current and future digital products. Firms can re-use internally developed IP cores in their own products or they can gain revenues through licensing, royalties, and customisation of these pre-designed components. There are over 150 European firms that sell licences to their IP cores. At present, the globally leading vendor is the ARM Holdings plc, based in the UK, whose IP cores were used in about every fourth programmable electronic device manufactured in 2007.

As technology allows now billions of transistors on one semiconductor die, it is impossible to build new chips from scratch. Instead, designers start with large libraries of semiconductor IP and construct new chips by combining, modifying, and complementing earlier designs. Often dozens or more IP blocks are combined in one chip to create Application Specific Integrated Circuits (ASICs), Application Specific Standard Products (ASSPs), and complete Systems-on-Chip (SoCs). These, in turn, provide the foundation for products such as mobile phones, television desktop boxes, digital cameras, MP3 players, automobile engine and industrial process controllers, toys, smart cards, hearing aids, heart monitors, and basically everything that uses or processes information and data.

As the design of IP cores often requires expertise both in microelectronics design and demanding application domains, specialised firms that develop IP cores represent a highly knowledge-intensive segment of the ICT industry. IP cores are used in almost all new semiconductor chip designs, and they are critically important for the successful introduction of new electronics products. The future of this industry segment is therefore of major importance to the European information economy.

In the history of the semiconductor industry, manufacturing, assembly and testing activities have relatively rapidly moved to countries with low manufacturing costs. Today, with the exception of Intel, IBM, Samsung and few other Integrated Device Manufacturers (IDMs), the actual manufacture of semiconductor chips is dominated by firms located in Taiwan, China, and Singapore.<sup>2</sup> Also Intel and IBM are increasingly producing leading-edge semiconductors in Asia. Intel started the construction of its first semiconductor manufacturing plant in China at the end of 2007, investing \$2.5 billion in the project. In December 2007, IBM, in turn, licensed its advanced 45 nanometre technology to SMIC, now globally the third-largest independent semiconductor manufacturer, based in China. The present study, therefore, also discusses the current and potential geographic relocation of design activities of semiconductor IP cores, and its possible policy implications.

The semiconductor industry is today in a historically unique situation. For almost five decades the industry has been driven by

<sup>2</sup> In 2007, the Taiwanese TSMC and UMC, the Chinese SMIC, and the Singaporean Chartered Semiconductor were the leading independent semiconductor foundries, with a market share of 71 per cent.

continuous miniaturisation. The size of transistors on semiconductor die is now measured in nanometres. The smallest features on leadingedge chips are now down to three atomic layers. As the cost of manufacturing has remained almost constant per square millimetre, transistors are now tens of millions times less expensive than they were just three decades ago.

This improvement is a key factor in the emergence of the information economy and knowledge society. The predictability and constancy of improvements in the semiconductor industry has defined business logic in the industry and also widely beyond it. Many industries now explicitly or implicitly rely on continuous technical progress in the semiconductor industry. In the near future, this fundamental driving force will evaporate. Miniaturisation is becoming increasingly expensive, its technical and economic benefits are declining, and new alternative sources of value are emerging in the knowledge economy.

This technical discontinuity will have huge implications. It will show up in macroeconomic indicators of productivity and growth, and it will make us ask why, exactly, smaller transistors were considered to be better. At the same time, new business models will emerge, and new sources of value will be defined and appropriated. Value added in design is becoming increasingly important as incremental technical improvement slows down. The present study claims that to understand the emerging opportunities, we need to understand the "chipless" model, which focuses on creating re-usable intellectual property blocks and processing architectures.

Semiconductor IP represents a very knowledge-intensive part of the ICT industry, and one of its highest value-adding activities. Basically, it packages and resells pure knowledge. Changes in the semiconductor IP sector, therefore, are potentially important for the USD 1.5 trillion electronics industry, as well as for the rest of the knowledge economy.

#### 2.1.1. European Intellectual Property Architectures in the Global Context

Europe is today a relatively strong player in the semiconductor IP field. Although European and global semiconductor firms now manufacture many of their products in Asia, Europe has several leading IP firms and over 150 small IP vendor firms. The semiconductor wafer manufacture is now dominated by dedicated Taiwanese, Chinese and Singaporean firms, and also large IDMs now increasingly outsource wafer production to Asia. The leading edge general-purpose microprocessor production, in turn, is led by traditional integrated device manufacturers such as Intel, AMD, and IBM. Although semiconductor design is increasingly done in countries such as India, Europe still has strong capabilities in IP creation, and good possibilities to stay at the leading-edge in the semiconductor IP industry. European researchers have also developed new innovative processing architectures, and several semiconductor IP start-ups have been launched in the EU as a result of university research.

In geographical terms, the UK is the leading EU country in semiconductor IP, though successful IP firms exist in most EU countries. We describe the European IP vendors in more detail in subsequent chapters of this report. We also highlight some of the factors that have led to geographic concentration of semiconductor design activities on the global and European levels.

Although this study estimates that the revenues generated by the chipless semiconductor firms are less than one percent of the total semiconductor industry, it is important to understand the reality behind the numbers.

First, the semiconductor IP industry creates inputs for the semiconductor industry. It is

13

therefore not possible to estimate the economic impact of semiconductor IP simply by comparing these two industries using their revenues. In fact, the size of the IP market should be compared with the semiconductor design services market. The semiconductor IP industry is essentially about semiconductor designs that are sold as prepackaged products. Often the package comes with consulting and customisation. At one extreme, the design work is done to the specifications of a customer. In that case, market analysts categorize the activity as design service. When the design is sold as a licence to use and copy a design component, the activity is categorised as IP.

Gartner Inc. estimates that the global semiconductor design services revenue in 2008 was about USD 1.7 billion. This is almost exactly the size of the chipless semiconductor market. In other words, about half of the semiconductor design market consists of design services and about half pre-designed IP blocks. As IC design houses also extensively reuse their internally developed IP blocks, the exact proportions of revenues are, however, quite impossible to estimate accurately.

Second, the majority of commercially used semiconductor IP is not visible. For example, Semico estimates that about four or five times more reusable IP blocks are developed internally than are sold on the market. The volume of reusable IP design activities, therefore, may well be five times bigger than market studies estimate. As the processes for managing and packaging IP blocks mature inside semiconductor firms and as it becomes increasingly necessary to create reusable IP as the complexity of designs increase, this internally developed IP can relatively easily be used to create additional revenues. Potentially, the visible IP market could rapidly increase as such internal IP would enter the market.

In general, IP creation is among the highest value adding activities in the ICT production, and its economic impact is often grossly underestimated. The semiconductor IP segment, therefore, represents interesting policy and business opportunities, as the ICT industry enters a period of technical disruption in the next years.

#### 2.2. Scope of the Study

In the present study we define intellectual property cores as pre-designed components that can be combined with other design elements to form a functional system. Traditionally, IP cores have been implemented on semiconductor die, either in Application Specific Integrated Circuits (ASICs), or on Field-Programmable Gate Arrays (FPGAs).<sup>3</sup> Emerging technologies, such as printed organic electronics, however, can potentially also be used to implement IP cores in the future. Although the focus of the study is on semiconductor IP cores, it also takes into account developments occurring beyond the present semiconductor industry.

New technologies, including carbon nanotubes, graphene transistors, self-organising molecular devices, and quantum computing can potentially bypass the physical limits of known semiconductor technologies. Eventually, such radical new technologies could substitute current technologies and enable progress in ICTs. The present study does not discuss these future technologies in any detail, for a very simple but important reason: it starts from the observation that even if radical new technologies were available today in industrial volumes, their deployment would require knowledge, manufacturing technologies, and design methods and tools that are radically different from those currently used in the semiconductor industry. The underlying claim is a rather strong one. Even if, for example, new carbon-based transistors and full-scale manufacturing methods for them existed today, the industry would still face a

<sup>3</sup> The appendix describes ASIC and FPGA design processes in more detail.

major technical disruption that would rewrite the rules under which it has operated for the last several decades. This disruption will occur irrespective of whether the new technologies are there today, or in thirty years time. Although the full story is obviously more complicated, the present study empirically focuses on the current industrial reality and simultaneously argues that the continuous progress that characterised the development of ICTs is about to end. The analysis of future developments in the semiconductor IP industry is therefore based on charting the current business landscape and generic patterns of technology development, instead of focusing on possible scientific breakthroughs and innovative new technologies. A further justification for this approach is that there are no known alternatives for the currently used technologies that could be manufactured in industrial volumes in the foreseeable future.

The specific empirical focus of the present study is on IP cores that can be programmed and combined into larger processing architectures. The study defines such IP cores as *IP computing cores*. These are, typically, programmable microprocessors, micro-controllers, digital signal processors, analog-digital mixed-signal processing blocks, and configurable computing architectures. As computing cores typically require additional IP components to create a fully functional chip or a system-on-chip, these complementary components are also taken into account when relevant.

For the purposes of the present study, it is not necessary to categorise different types of semiconductor IP in any great systematical detail, although it is useful to understand that different economic constraints and innovation dynamics underlie different IP product segments. In practice, market analysts often distinguish many different types of IP to segment the market and to cluster vendors. Such segmentation is not trivial, and methodological differences sometimes lead to widely varying estimates of IP markets. In practice, IP is packaged in many ways, vendors continuously develop their business models, and entries, exits and mergers change the business landscape so fast that data is barely comparable across the years.

Market studies sometimes differentiate between two types of semiconductor intellectual property: design IP and technology licensing. Technology licensing is used to transfer rights to use patented inventions. Design IP, in turn, consists of documented designs that the licensor can use as components in the licensor's own designs. According to preliminary data from Gartner Inc., the global semiconductor design IP market was USD 1.486 billion in 2008, whereas semiconductor IP technology licensing was worth USD 586 million.<sup>4</sup> The various semiconductor IP categories used by Gartner are shown in Table 1.

In the present study, we use a wide variety of market studies, industry reports, business news, and primary data collected on IP firms and their activities. We have also conducted several case studies that focused on the histories and growth patterns of selected IP firms. Going beyond a simple description of the current state of the IP segment, we also interpret the current situation and future developments in the broader contexts of globalisation and technology and innovation studies.

In the next chapter, we discuss major socioeconomic trends, as economies, products, and organisations enter the new knowledge-based era. We focus on the challenges of traditional intellectual property, new innovation models, and policy. Semiconductor "intellectual property" is often a misleading term, as it tends to put the semiconductor design segment into a context

<sup>4</sup> The data is a preliminary estimate for 2008. One should also note that the numbers do not add up. The total volume of the various IP segments in the table is USD 1,540 million. Assuming that technology licensing is counted as a separate IP category, the total market would be 2,127 million.

| T. Schneonductor in in 2008, as categorised by Garther inc. |                                  |              |          |

|-------------------------------------------------------------|----------------------------------|--------------|----------|

|                                                             |                                  | USD millions | Growth % |

| Processors                                                  | Microprocessors                  | 582          | 6.2      |

|                                                             | Digital Signal Processors        | 52           | 21       |

| Physical IP                                                 | Analog and Mixed Signal          | 205          | 22.4     |

|                                                             | PHY                              | 149          | 8.4      |

|                                                             | Memory cells/blocks              | 132          | 4        |

|                                                             | Physical library                 | 62           | -6       |

| Other IP                                                    | Fixed function signal processing | 182          | 16       |

|                                                             | Interface controllers            | 79           | 5.5      |

|                                                             | Block libraries                  | 29           | -16.5    |

|                                                             | Infrastructure IP                | 34           | 3.1      |

|                                                             | Miscellaneous IP                 | 28           | -11.4    |

|                                                             | Controllers and peripherals      | 6            | -15.2    |

|                                                             | Total design IP                  | 1486         | 8        |

|                                                             | Technology licensing             | 587          | 6.8      |

|                                                             | Total IP                         | 2073         | 7.7      |

where the concept of intellectual property and intellectual property rights would be central. This is rarely the case in practice, as can be seen during the following chapters. Yet, the semiconductor IP segment is characterised by the fact that it trades intangible assets, and the structures of intellectual rights regimes are important for its future. We highlight some key issues, and provide some references for further discussions. Similarly, we briefly revisit some key themes of recent innovation research, as they inform and underlie various sections of the report, including its policy proposals. The chapter also discusses the possibility that the wide use of ICTs has actually changed the fundamental conditions for making policy. We frame this discussion in the context of long waves of economic growth and the impact of key technologies, showing how developments in the semiconductor technology potentially destroy the historical patterns of growth and crisis, also known as the Kondratieff waves. The aim of the chapter is to give some perspective to the rest of the study and to help the reader think about changes that occur outside the semiconductor industry that could shape its future in important ways.

Chapter 4 switches from this conceptual discussion to a more data-oriented approach. It

describes the current reality of the semiconductor industry, describing its business models and value creation activities both in qualitative and quantitative terms. We then focus on the semiconductor IP industry itself, providing data on the IP market and supply, including geographic patterns of production. To get a better understanding of what typical IP firms actually do, we provide a detailed description of Swedish IP firms and a brief outline of the historical development of the largest IP vendor, ARM Ltd.

Chapter 5 describes in details the IP market, its suppliers and consumers. It gives comparative data for different geographical regions and offers a more in-depth view of the Swedish IP vendors as well as of ARM Holdings, the worldwide leading company whose headquarters are based in UK.

Chapter 6 moves to the main historical drivers in the semiconductor industry, first focusing on the continuous miniaturisation and its impacts, and then discussing economic trends and patterns of internationalisation. In discussing the historical development of internationalisation, we highlight the factors that underlie the prominence of Silicon Valley and East Asia as global hubs in semiconductor production. Based on innovation and technology studies, we then try in the following Chapter 7 to uncover major drivers that could shape the future of semiconductor IP and information processing architectures. The chapter is obviously speculative in nature, as we talk about generic trends that cannot be verified at this point in time. Specifically, we discuss the future of Makimoto Waves that have been claimed to drive the industry through cycles of standardisation and customisation. We also propose a new model that links reconfigurable IP architectures to usercentric innovation models.

One question of intrinsic interest to regional policymakers is the potential of China as a semiconductor IP creator. In the history of semiconductors, production tasks and segments of value chains have rapidly moved to East Asia and, more recently, to China. We describe in Chapter 8 the status of the IC design segment in China, highlight some recent policy issues, and evaluate five possible trajectories that could make China a prominent IP actor.

Finally, in its last chapter, the report suggests several policy implications. We present a generic model of entry and exit in the IP segment, and use it to highlight key areas where policy could make a difference. These include new approaches for competence development, expanded access to design tools in open development ecosystems, and new low-cost realisation paths for designs and experimentation. We further highlight the need for new computational models, including reconfigurable hardware processing architectures, and suggest that latent opportunities could be made visible and explicit by a new type of roadmap activity organised around small IP vendors and developers. We also point out some potentially important areas for policyrelated research. These include new approaches for regional policies that facilitate the growth of local hot-spots in global innovation ecosystems, and research on the enablers of the open source development model in the hardware domain. The latter we consider important, as the open source model has shown its potential to lead to very fast growth in the software domain, as well as its capability to reorganise existing industries and business logic.

# **3. Emerging Discontinuities**

In the next years, the semiconductor industry is about to experience a major discontinuity, with vast economic and social ramifications: The end of scaling of the physical dimensions of components on integrated circuits. When Jack Kilby created the first integrated circuit in 1958, it contained two transistors and a couple of other components.<sup>5</sup> Today it is easily possible to package tens of millions of transistors on a chip of same size. For fifty years, engineers have found ways to print smaller and smaller features on silicon wafers. As chapter 2 describes in more detail, in the second half of 1990s, when the developments in optical lithography were exceptionally fast, the physical dimensions of the smallest component features declined 30 percent every two years. This implied halving of the component area requirements in about the same time.

In high-volume semiconductor components, such as microprocessors and memory chips, this technical advance has been translated into rapidly declining component costs. In the second half of the 1990s, the cost of a transistor on a microprocessor chip declined 60 percent, annually. This was exceptionally fast, but typically the declines of quality adjusted prices have been over 40 percent on annual basis.

We can imagine an economic crisis, where the stock market value drops 50 percent in a year, resembling what we saw in 2008. Then we have to imagine that this crisis continues without abatement, 35 years. That gives a rough scale of the change that has occurred in the semiconductor processor industry. The end of semiconductor scaling will therefore be a major technical disruption. It will also occur at a time when it is possible to package more transistors on a chip than most applications need, and also more than designers are able to effectively use. As Bass and Christensen noted some years ago:

"This is precisely the juncture at which the microprocessor market has now arrived. Price and performance, fuelled by the industry's collective preoccupation with Moore's Law, are still the metrics valued in essentially all tiers of the market today. Even so, there are signs that a seismic shift is occurring. The initial, performance-dominated phase is giving way to a new era in which other factors, such as customization, matter more."<sup>6</sup>

Although commentators of the industry tend to highlight bleeding-edge advances in the industry, the real action is often elsewhere. Strictly speaking, the most advanced semiconductor technologies are used for niche products. Although the cost of transistors has radically declined during the last six decades, a low-cost transistor on a bleeding edge semiconductor chip now costs over 50 million USD to create. Basic economics means that these chips can only be used for products that can be sold in tens of millions of copies. It may be odd to call these products niche products, as hundreds of millions of consumers use PCs, DVDs, digital set-top boxes, MP3 players, digital cameras, and mobile phones.<sup>7</sup> In practice, however, bleeding edge technologies are used only in a small number

<sup>5</sup> Kilby's patent application, filed in February 1959, shows two transistors, eight resistors, and two capacitors. Robert Noyce, from Fairchild Semiconductor, filed a patent in July the same year, with one transistor, two diodes, three resistors, and two capacitors. The Noyce patent became the foundation of the planar process of making integrated circuits.

<sup>6</sup> Bass & Christensen (2002, 35).

<sup>7</sup> According to estimates from Gartner, Inc., in 2007 the top ten original equipment manufacturers accounted for USD 91 billion of semiconductor consumption, or about a third of the total. The biggest semiconductor users were Hewlett-Packard and Nokia. Today, about two-thirds of semiconductors are used for PCs and mobile phones.

of high-volume products, and very many digital products are built using technologies that were new ten or twenty years ago. The most technically amazing advances in semiconductor technology, therefore, tend to be irrelevant for many potential users of information technology. More importantly, great potential for future innovations in ICTs can be found from this "long tail" of semiconductor technology, as discussed in Chapter 6.

Christensen, quoted above, is known for his research on disruptive technological change in the computer industry. According to Christensen, the leading firms tend to fail and new entrants usually become industry leaders when the underlying technology does not improve incrementally.8 A recurring pattern in many technologybased industries, including mainframe, PC, and automobile production, has been that the source of competitive advantages moves from performance to reliability, then to convenience and finally to customization. When performance starts to exceed user requirements, the market becomes segmented into tiers, where only few customers are focusing on high performance at any cost. Most customers are willing to trade off cost and performance. Further, the product characteristics that customers were willing to pay for shift from leading-edge performance to reliability, convenience and customization. Bass and Christensen conclude that:

"The fact that microprocessor designers are now 'wasting' transistors is one indication that the industry is about to re-enact what happened in other technology-based industries, namely, the rise of customization. ...Modular designs by definition force performance compromises and a backing away from the bleeding edge."<sup>9</sup>

On a more macroeconomic scale, the discontinuity created by the end of scaling will

match the neo-Schumpeterian interpretations of long waves in economic growth and productivity. The end of scaling, therefore, could be interpreted as the end of the most recent Kondratieff wave.<sup>10</sup> Below we argue, however, that advances in the semiconductor industry have been profound enough to break the historical patterns that created the Kondratieff waves, making semiconductor IP an especially interesting opportunity for future growth.

#### 3.1. The New Paradigm of Knowledge Economy

The present study focuses on intellectual property -based business models in the semiconductor industry. IP-based businesses rely on copyrights and patents, as they need to publish specifications of their knowledgebased products. The actual licensing agreements are made between known parties, and can therefore be completed as normal business contracts. Intellectual property rights, however, are important for protecting created knowledge and products against unauthorized copying and use. Technical and legal protections for IP are therefore actively developed and promoted by semiconductor industry firms and associations. Until recently, many semiconductor firms have, for example, been reluctant to locate design activities in China due to the perceived lack of IPR enforcement and protection.

The protection of outputs of the IP industry is an important issue for IP vendors. More fundamentally, however, the IP-based industry is a knowledge-based industry, where the critical inputs are intellectual assets. It is fundamentally an industry driven by innovation. To understand the IP-based business models and their economic impact, we, therefore, have to adopt a broad view

<sup>8</sup> Cf., Bower & Christensen (1995), Rosenbloom & Christensen (1994), and Christensen (1997).

<sup>9</sup> Bass and Christensen (2002).

<sup>10</sup> Kondratieff waves in economic development have usually been described as large-scale fluctuations in global economic growth patterns that last about 40 to 60 years. For references and discussion, see section 3.3.

Source: WIPO, 2007

on intellectual assets generated in the industry. Some of these are traditional intellectual property assets; the role of traditional IPR, however, is also becoming less visible as design firms focus on continuous rapid innovation and the development of innovation ecosystems.

Today, intellectual assets are still rarely included in national and business accounts.<sup>11</sup> Typically, investments in knowledge are interpreted as final or intermediate consumption. Preliminary estimates in countries such as Finland, Japan, the U.K., the Netherlands, and the US put the annual investments in intellectual assets at around ten percent of GDP.<sup>12</sup> In the US, the investments in intangible assets exceeded the investments in tangible assets in the 1990s, and in the late 1990s, the US non-farm output was underestimated by about 1 trillion USD and the business capital stock by 3.6 trillion USD due to the invisibility of investments in intellectual assets.<sup>13</sup>

The estimated size of the knowledgebased economy is now rapidly growing, both because knowledge is becoming visible in the national and organizational accounting systems but also because business success is becoming increasingly dependent on knowledge and innovation. One indication of this is the increasing patenting activity around the world. According to the 2007 Edition of the WIPO Patent Report there

<sup>11</sup> Intellectual assets are often defined to include investments in research and development, patents, software, human skills, and structural and relational capital in organizations.

<sup>13</sup> Corrado, Hulten, Sichel (2005; 2006). Corrado et *al.* estimate that "bricks and mortar" investments accounted for less than 8 percent of total output growth per hour in the period 1995-2003 in the US. Corrado *et al.* Categorize intellectual asset investments into three major groups: computerized information, innovative property (R&D and design), and economic competences that include brand equity, firm-specific human capital and organizational capital. All these forms of assets clearly depend on ICTs.

were approximately 5.6 million patents in force worldwide at the end of 2005, and more than 1,6 million applications were filed in the same year. As can be seen from the Figure 1, the fastest growth in patent applications was in China.

Whereas patents represent one output of the knowledge economy, research and development is one of its key inputs. In the OECD countries, R&D expenditure climbed to USD 817.8 billion in 2006, up from USD 468.2 billion in 1996. In real terms, R&D spending grew at between 3.2 and 3.4 percent a year from 1996 to 2006. In the present decade, China has rapidly grown its R&D expenditures. In 2006, China's gross domestic expenditure on R&D (GERD) reached USD 86.8 billion, or about one third of EU GERD at the same year.<sup>14</sup>

The concept of intellectual property is not a trivial one, and some sophistication is needed when policies are developed in IP-related domains. Knowledge is not a "thing" that can be possessed and owned as material assets. Knowledge gains and loses value in social and material contexts, and it also reflexively changes those contexts. In general, new knowledge potentially changes the underlying systems of value.<sup>15</sup> Classical economic concepts, therefore, can not in any straightforward way be used to analyze knowledge economy. Knowledge is also an inherently social and relational phenomenon. Knowledge is embedded in culturally meaningful technologies and social practices. The concept of intellectual property, therefore, is in many ways theoretically broken, and it easily misses many characteristics that are important when we try to understand knowledgebased economy.<sup>16</sup> Yet the concept originates from concrete social and economic problems that need to be addressed also today.

14 Data from (OECD 2008b).

0 Thermical Report Series

The Statute of Anne, which laid down the modern principles of intellectual property rights in 1710, aimed at balancing two conflicting interests: the wide diffusion of new knowledge for the benefit of the society, and the economic interest of the creator of the new knowledge. The Statute solved this problem by granting the creator the monopoly rights for copying books for fourteen years, after which the knowledge was put in the "public domain," where it was freely available for anyone.17 The Statute noted that frequent copying without the consent of authors or proprietors had lead to their "great detriment, and too often to the ruin of them and their families." On the other hand, the monopoly was limited, as monopolies were considered to be harmful, for example, because they were usually associated with artificially high prices.<sup>18</sup>

The Statute of Anne focused on copyrights. Following its logic, the broader concept of "intellectual rights" was introduced in the U.S. Constitution in 1787.<sup>19</sup> Intellectual rights became known as intellectual property rights as publishers started to argue that authors have "natural rights" to the ownership of their works. Publishers argued that intellectual rights should be perpetual, as they were a form of property.<sup>20</sup> This view was particularly influential in France, where, for example, the Paris Book Guild hired the encyclopaedist Denis Diderot to write a treatise that would promote the Guild's interest in literary rights.<sup>21</sup>

<sup>15</sup> Tuomi (1999).

<sup>16</sup> For an overview, see, e.g., Jaffe and Lerner (2004).

<sup>17</sup> The copyright monopoly could be extended for another fourteen years if the author was still alive when the original copyright period expired.

<sup>18</sup> The Statute therefore also included a clause that enabled anyone to make a complaint if the price of the book seemed to be artificially high (Tuomi 2004a).

<sup>19</sup> Specifically, the Constitution stated: "the Congress shall have the power...to promote the progress of science and useful arts, by securing for limited times to authors and inventors the exclusive right to their respective writings and discoveries."

<sup>20</sup> Ewing (2003).

<sup>21</sup> Diderot argued that intellectual property was the highest form of property. He asked: "What form of wealth could belong to a man, if not a work of the mind...if not his own thoughts...the most precious part of himself, that will never perish, that will immortalize him?" (Ewing 2003).

The justifications and the impact of intellectual property laws, therefore, have been debated for long time.<sup>22</sup> In recent years, the debate has again been very active. Many experts now claim that the intellectual property system is seriously flawed. For example, many innovations are system innovations that cumulatively build on earlier innovations and knowledge. When monopoly rights are granted for such incremental system improvements, they tend to constrain future innovation, instead of promoting it. This happens particularly in domains where technology develops fast and product life-cycles are short. Semiconductor IP blocks are often used in such system settings, and IPR regimes can therefore have strong influence on patterns of technology development in this domain. The intellectual property system is also widely used against its original intent. For example, the US patent system allows applicants to postpone the issue of a patent and keep it secret until someone else builds a business on the same idea. Such "submarine" patents have frequently been used to create extraordinary returns also in the semiconductor industry.23 The innovative quality of granted patents is frequently questioned, in particular in domains such as software development, where innovation is typically based on relatively straightforward engineering work and where prior art has not been systematically archived. In such environments, patents often act mainly as barriers for competition. This is a major problem for small firms and innovators who are not able to use their existing patent portfolios for cross-licensing.24

Although it is difficult to revise existing intellectual property regulation, business firms are now actively experimenting with models that could overcome some of the problems in the current IPR regimes. For example, many firms are now trying to use open innovation models.<sup>25</sup> The underlying logic is based on the idea that modern ICT makes it possible to create large innovation ecosystems where value is created by continuous and rapid innovation. As the global innovation system is now producing innovations at high rates, the value of intellectual property monopolies tends to decrease, and in many industries the competitive edge can only be created by innovating faster than the competitors. For many technologies, such as software, the time of securing patent monopoly often exceeds the product lifetime, thus making the benefits from patents questionable. Furthermore, as the enforcement of patent rights tends to be very expensive and difficult, many firms now experiment with business models where intellectual property is not monopolized. For example, Sun Microsystems now licenses the designs of its SPARC microprocessors using an open source license. In the software domain, this open source approach, of course, has been widely used, and, for example, both Google and Nokia license their mobile phone operating systems as open source software.

<sup>22</sup> See, e.g., Machlup and Penrose (1950).

<sup>23</sup> Graham (2006).

<sup>24</sup> Cf. Shapiro (2001), Hall & Ziedonis (2001), Samuelson (2004). For example, Hall and Ziedonis (2001:110) quoted an estimate that a new semiconductor manufacturer should have spent \$100 to \$200 million of revenues to license what were considered basic manufacturing principles but which did not transfer any currently useful technologies. This, in practice, makes entry impossible for firms who do not have extensive patent portfolios with which they can bargain.

<sup>25</sup> The concept of open innovation has been promoted by Chesbrough and refined with his especially (Chesbrough colleagues 2003; Chesbrough, Vanhaverbeke, and West 2006). The key starting point for Chesbrough was corporate R&D, IPR management, and the observation that an increasing amount of knowledge exists and is generated outside the focal firm. In this sense, Chesbrough's open innovation concept aligns with the earlier knowledge management literature that emphasized the importance of intellectual capital (including customer and network capital) as a key productive asset in knowledge-based firms (e.g., Wiig (1993), Sveiby (1997), Edvinsson & Malone (1997), Roos et al. (1997), Brooking (1996)). The realization that key knowledge sources exist outside the focal firms also underlies knowledge management and innovation literature that focuses on organizational learning (e.g. Brown & Duguid (1991; 2001)), organizational knowledge creation (e.g. Nonaka & Takeuchi (1995)), and organizational networks (e.g., Powell et al. (1996), Hastings (1993)). An alternative model of open innovation is based on user-centric innovation models. We discuss these in the next section.

#### 3.2. Innovation Communities and **Ecosystems**

The importance of distributed networks has been one of the leading themes in recent innovation research. The traditional view on innovative activity emphasized "heroic innovators," who developed their ingenious insights into new products and services. This model was adapted to organizational product development, which was managed as a fundamentally linear sequence of phases that led from ideas to finished products and their eventual diffusion in the marketplace. More recently, it has been realized that the process is highly iterative and that users are also important sources of product development knowledge.26 Current research on innovation and product creation has therefore moved toward "open" innovation models that extend the innovation process beyond firm boundaries and "downstream" innovation models, where users actually become the focus of innovation.27

In the theoretically strongest interpretation of downstream models, innovations materialize when social practices change and when latent technical opportunities are taken into use in the society.28 Such downstream models have their roots in empirical research on technology adoption and also theoretical and empirical studies on social learning and knowledge creation. We briefly introduce some key ideas underlying this view, as these new models of innovation have potentially important consequences for both business and policy development.

In strong downstream models, "upstream" innovation is taken for granted. This approach may at first look counter-intuitive and radical. It is, however, supported by many detailed studies of technology development. Upstream innovation, in fact, rarely represents a bottleneck in the innovation process: Instead, reinvention and parallel discovery typically dominate in the upstream, and innovative ideas are often overabundant. This is not always immediately obvious, as historical retrospection tends to sketch linear paths of progress, often adjusting historical facts to make a story that fits our expectations of how innovation should happen.<sup>29</sup> At the same time, historical accounts obscure the fact that firms and scientists rarely create new ideas. Downstream innovation models are based on the observation that, in practice, the key bottleneck is in the social adoption of latent innovative opportunities.

In the strong downstream models, the users are perceived, not as individualistic consumers, but as members of social communities that maintain specific pools of knowledge and related practices that make new technological opportunities meaningful.<sup>30</sup> In contrast to traditional models of innovation, the focus of innovation, therefore, is perceived to be on the

28

ical Report Series

<sup>26</sup> Von Hippel (1988) focused on the role of users as sources of new knowledge and product innovations.

This includes von Hippel's recent work, where he has emphasized the importance of distributed innovation models (e.g., Von Hippel 2005; Lakhani and von Hippel 2003; Von Hippel and von Krogh 2003). Along similar lines, a more theoretically grounded model was presented by the current author (Tuomi 2002a), who studied the evolution of Internet-related innovations, including basic networking technologies and the Linux operating system. This downstream innovation model was based on the observation that the focus of innovation can increasingly be found from user communities who actively reinterpret and reinvent the meaning of emerging technological opportunities. Similar emphasis on users as innovators can be found in studies on social construction and domestication of technologies (for a review of these, see Oudshoorn & Pinch (2003)). Tuomi (2002a).

For example, official histories of the emergence of packet-29 switching computer networks and the Internet reorganize events in time and selectively forget facts that do not fit the linear story line (Tuomi 2002a, chap. 9).

<sup>30</sup> We contrast here "user-innovator" and "pure" downstream models. In the user-innovator models (e.g. von Hippel), the users contribute new ideas to a quite traditional upstream innovation process. In the pure downstream models, innovation, in contrast, becomes a process of socio-technical change that occurs in social practices. Although "upstream" actors (e.g. business firms) can feed new technical opportunities into the process, innovation can also occur, for example, by reinterpreting and "misusing" existing products. Developments in computer and communication technologies, in fact, have often been driven by unanticipated uses.

innovative and creative activities that occur in the context of use.<sup>31</sup> One important locus of innovation can be found in communities of practice, where social learning and shared interpretations of the world provide the basis for knowledge creation.<sup>32</sup> Upstream and downstream innovators, therefore, are not simply individuals with bright ideas. Instead, innovation occurs in a social structure that consists of a network of specialized communities.<sup>33</sup> An important consequence of this view is that knowledge is not universal, and the world of knowledge is not "flat." ICT reduces barriers created by geographical distance; social boundaries, however, remain highly important for knowledge diffusion and production.<sup>34</sup>

Research on innovation communities has emphasized the fact that innovators rely on social networks and socially mobilized material and cognitive resources. Also cognition, itself, is often distributed among people and technical artefacts. This has important consequences for innovation management in business firms. For example, the downstream view highlights the point that informal social networks that cross organizational boundaries provide the foundation for the creation of new knowledge. Innovation management, therefore, can not be a purely internal affair in business firms; instead, it has to be based on strategic management of knowledge creation and knowledge flows that occur in the broader innovation environment.<sup>35</sup>

When different types of knowledge and expertise are combined and synthesized for new ideas and products, the continuously evolving innovation system can also be viewed as an ecosystem.36 Such a view on mutual coevolution of actors can result from a relatively straightforward metaphorical use of ecological concepts. At a more substantial level, it leads to fundamentally social views on technological development. Innovation is not something that happens inside firms. Instead, it is a process where many actors, ideas and technical artefacts co-evolve and provide resources and constraints for change. Most importantly, innovation can not be understood in any simple way as purely technical improvement, as improvement itself can only be understood in a social context that makes the underlying technology meaningful. Although in the industrial society this social context evolved relatively slowly, making it in many cases possible to forget and take for granted the social dimension of technology and innovation, today we live in a world where this rarely is the case.

# 3.3. Policy at the End of Kondratieff Waves

Innovation has been a somewhat awkward topic for many economists in the recent decades, as the neoclassical theory starts from equilibrium models that are, strictly speaking, incompatible with the idea of innovation. Innovation, therefore, has often been defined in economics as the

<sup>31</sup> The underlying theoretical foundations have been discussed in the contexts of knowledge management, innovation theory, and information systems theory by Tuomi (1999; 2002a; 2006).

The "community of practice" model was developed 32 in Lave and Wenger (1991), and applied in innovation and organizational learning context first by Brown and Duguid (1991). Nonaka and his colleagues have proposed an alternative model of the loci of innovation, based on the concept of "ba" that was originally developed by the Japanese philosopher Nishida (Nonaka, Toyama, and Hirata 2008). Ba, according to Nonaka et al., provides the shared dynamic context where new meaning and knowledge is created. In contrast to communities of practice, which are based on relatively stable social structures and technology-enabled practices, the concept of ba emphasizes more transient interactions among social participants. The underlying epistemic concepts are rather sophisticated, and have been discussed in detail in Tuomi (2002a; 2006).

<sup>33</sup> Brown and Duguid (2000; 2001), Tuomi (2002a).

<sup>34</sup> These social boundaries are essentially boundaries of local meaning systems. Social practices and local meaning systems are connected, for example, by boundary objects that are shared across communities of practice (Star and Griesemer 1989), and which include concrete artefacts, design schematics, and, for example, databases (Bowker and Star 1999, chap. 9).

<sup>35</sup> In this sense, downstream models share the starting point of "open innovation," as described by Chesbrough (2003).

<sup>36</sup> Cf., Moore (1996), and Hagel and Brown (2005).

unexplained component of growth.<sup>37</sup> Research on the economics of innovation, therefore, has often been influenced by socially and historically grounded theories of economy.<sup>38</sup> In recent years, a particularly influential stream of research has formed around studies inspired by the pioneering work of Schumpeter.

A basic question in the Schumpeterian framework is how innovation and technology influence economic growth. Schumpeter's early work focused on long-term economic growth patterns and their links to innovation. This pioneering work has led to a large body of neo-Schumpeterian literature that tries to explain large-scale patterns in the economic history by the underlying changes in key transport, communications, and production technologies.<sup>39</sup>

For example, Perez<sup>40</sup> has highlighted the point that the economic history can be understood as a sequence of techno-economic paradigms, where long-term growth periods have been driven by the wide application of a new general-purpose key technology. According to Perez, the statistically observable long waves of economic growth since the first Industrial Revolution to the emergence of steam power and railways, electrical and heavy engineering, mass production, and, most recently, microelectronics, have been associated with profound changes in the dominant production paradigms. The realization of the economic potential of a new general-purpose key technology requires mutual co-evolution and alignment of social institutions and practices, including legal frameworks, management practices, and industrial relations. Historically, the changes in techno-economic paradigms have

37 Solow's residue, which includes all those sources of productivity growth that cannot be explained, is the most famous example here. Economists have often defined technical progress as the factors that underlie Solow residue.

Technical Report Series

been associated with new sources of competitive advantage, new geographical growth patterns, and the decline of old economic centres.

important outcome of An the neo-Schumpeterian analysis lies in its observation that social change is the constraining factor when technological opportunities become transformed into economic value. Technology and the capabilities it affords can efficiently be integrated with social practices only after a gradual process of alignment. As a result, the diffusion of new technologies is strongly constrained by the speed of social and institutional change.<sup>41</sup> Policy, therefore, can also play a crucial role in this change. When new key technologies lead to radical changes in the modes of production, by definition, these changes do not occur easily, and they create conflicts among prevailing interests and powers. This, indeed, can be understood as the fundamental reason why the long waves of economy are long.42

The long wave model of economic growth is a controversial issue, and it has been debated for several decades, both on theoretical and empirical grounds.<sup>43</sup> One may, however, ask where are we in the wave of ICT-induced growth? Is the golden age in the future, or is it already in the past?

Indeed, it has been recently argued that we are currently experiencing the end of long waves. For example, Hagel, Brown and Davison argue that:

"Major technical innovations like the steam engine, electricity, and the telephone brought forth powerful new infrastructures. Inevitably, these disruptive innovations transformed industry and commerce, but

<sup>38</sup> For a discussion of earlier work on innovation and economic theory , see e.g., Rosenberg (1982).

<sup>39</sup> See Freeman and Louçã (2001).

<sup>40</sup> Perez (1985; 2002).

<sup>41</sup> This view, therefore, implicitly adopts the downstream innovation model discussed above.

<sup>42</sup> As Kuhn (1970)argued, dominant paradigms often change only after their proponents die.

<sup>43</sup> Influential contributions include, for example, (Freeman, Clark, and Soete 1982) and (Kleinknecht 1987). For a discussion on the earlier debates, see Mandel (1995, chap. 6)